```

Last name:

```

The use of examination aids (e.g., calculators) is prohibited. Answers can be given in German or English. Please refrain from using lead pencils and red ink pens.

- Q1. (10 points) **FSM in SystemVerilog:** Consider the finite state automaton specified in SystemVerilog below:

- (a) The table to the right specifies the output logic. Specify their respective logical formulas.

- (b) Show the corresponding ASM diagram of the automaton.

- (c) Show the structural diagram of the automaton featuring logic blocks, flip flops, and wires.

- (d) Name the type of automaton in this example. What is the name of the second type of automaton and explain the difference between them.

- (e) Change one value in the **out\_o** column to create the other type of FSM. The resulting automaton need not be functionally equivalent.

```

module state_machine(

input logic clk_i,

input logic reset_i,

input logic in_i,

output logic [1:0] out_o

);

logic [1:0] state_p, state_n;

always @(posedge clk_i or posedge reset_i) begin

if (reset_i) state_p <= 2'b00;</pre>

state_p <= state_n;</pre>

else

end

always Q(*) begin

case (state_p)

2'b00:

state_n = state_p + 2;

2'b01:

state_n = 2'b11;

2'b10:

state_n = state_p - 1;

default: state_n = 0;

endcase

end

always Q(*) begin

// output logic is left out (refer to the table above)

end

endmodule

```

| state_p |     | in | out_o |     |

|---------|-----|----|-------|-----|

| [1]     | [0] |    | [1]   | [0] |

| 0       | 0   | 0  | 1     | 0   |

| 0       | 0   | 1  | 1     | 0   |

| 0       | 1   | 0  | 0     | 0   |

| 0       | 1   | 1  | 0     | 0   |

| 1       | 0   | 0  | 1     | 1   |

| 1       | 0   | 1  | 1     | 1   |

| 1       | 1   | 0  | 0     | 0   |

| 1       | 1   | 1  | 0     | 1   |

$\rightarrow$

## Q2. (10 points) **Pipelining:**

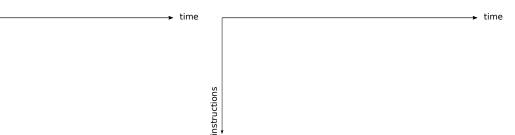

- (a) Explain the motivation and concept of pipelining based on the following example. You have a single cycle machine with a critical path of 600ps. You are able split the path into three pipeline stages of 200ps each. What does it mean to insert a pipeline stage? Explain how this leads to a speedup. How much is the speedup (assuming a full and ideal pipeline)?

- (b) Assume the three pipeline stages IF, ID (includes reading the operands from the register file), and EX. This pipeline executes the three instructions below. Explain the problem arising in the pipeline with this code snippet. Explain two approaches to resolve this problem.

- (c) Complete the diagrams below for both approaches and show which pipeline operation is performed at what clock cycle for each instruction of the code snippet. Assume an empty pipeline before starting the execution. State the total number of needed clock cycles for the execution of the code snippet for both approaches.

- (d) Motivate the need of a reorder buffer and explain its basic concept.

**ADDI** x2, x1, 0 # I1**ADDI** x3, x1, 5 # I2**ADDI** x4, x3, 3 # I3

nstructions

## Q3. (10 points) Assembly:

- (a) What is a calling convention and why is it needed? Explain what a calling convention covers.

- (b) Transform the following C-code to RISC-V assembly. All local variables of the C-code must be allocated on the stack. The global variable g is located at address 0xF00. The RISC-V calling convention must be followed. The assembly startup code including the initialization of the stack is provided below. Write the assembly code for the two functions at the foreseen locations.

| // Located at memory address 0xF00 | Assembly Reference |              |

|------------------------------------|--------------------|--------------|

| int g;                             | LW                 | rd,imm(rs1)  |

| <pre>int add(int* p) {</pre>       | SW                 | rs1,imm(rs2) |

| return *p + g;                     | ADD                | rd,rs1,rs2   |

| }                                  | ADDI               | rd,rs1,imm   |

| <pre>int main() {</pre>            | SUB                | rd,rs1,rs2   |

| g = 2;<br>return add(&g);          | JAL                | rd,imm       |

| }                                  | JALR               | rd,imm(rs1)  |

| start:<br>ADDI sp., zero., 0x700   | main :             |              |

| JAL ra, main                       |                    |              |

| EBREAK                             |                    |              |

|                                    |                    |              |

add:

## Q4. (10 points) Link Layer:

- (a) What are the advantages/disadvantages of circuit and packet switching? [4pt]

- (b) What does MAC and LLC stand for? [2pt] What is the purpose of LLC? [1pt]

- (c) Explain how CSMA/CD works [3pt]

## Q5. (10 points) **HTTP**:

Various application-level technologies enable advanced communication between server and client. Answer the following questions about them:

AJAX Name one of the precursor technologies [1pt]. Which programming language can be used to issue XMLHttpRequests? [1pt] Which problems does AJAX suffer from? [3pt]

Long Polling How does it work? [2pt]

WebSocket Name one advantage of WebSocket in comparison to AJAX [1pt]. Name one port used to handle WebSockets communication [1pt]. Is communication synchronous or asynchronous? [1pt]